# Reducing the Substrate Losses of RF Integrated Inductors

Ferenc Mernyei, *Member, IEEE*, Franz Darrer, Matthijs Pardoen, *Member, IEEE*, and Andreas Sibrai, *Member, IEEE*

**Abstract**—This letter introduces a new method for reducing the substrate-related losses of integrated spiral inductors for radio frequency (RF) applications. Measurement based equivalent circuit parameters are demonstrated. Using our method the quality factor increased from 5.3 to 6.0 at 3.5 GHz at an 1.8-nH inductor.

**Index Terms**—Integrated inductor, on-chip spiral, quality factor, substrate loss.

## I. INTRODUCTION

AT SILICON radio frequency (RF) integrated circuits, the usage of on-chip inductors in *LC* tanks is limited by the achievable quality factor. The modeling of such structures was carefully investigated [1], [2], and the source of losses were described as well [3], [4]. To find the optimal geometry, several “guidelines” were defined [2], [3] and optimizing algorithms were established in computer programs [5]. We can find the optimal line width for the highest possible quality factor for a given size and inductance value at a given frequency, but there have not been any suggestions published yet on how to reduce the substrate-related losses.

## II. REDUCING THE SUBSTRATE LOSSES

By optimizing the spiral geometry, we will end up with a line width which will move the maximum of the  $Q(f)$  curve to the desired frequency. In this case, the ohmic losses and the substrate capacitance will give us the minimal effective resistivity  $R_{\text{eff}}$  (where  $Z_{\text{in}} = R_{\text{eff}} + j \omega^* L_{\text{eff}}$ ). The substrate used to be considered a limiting factor that we could not change, or that we had to remove [6].

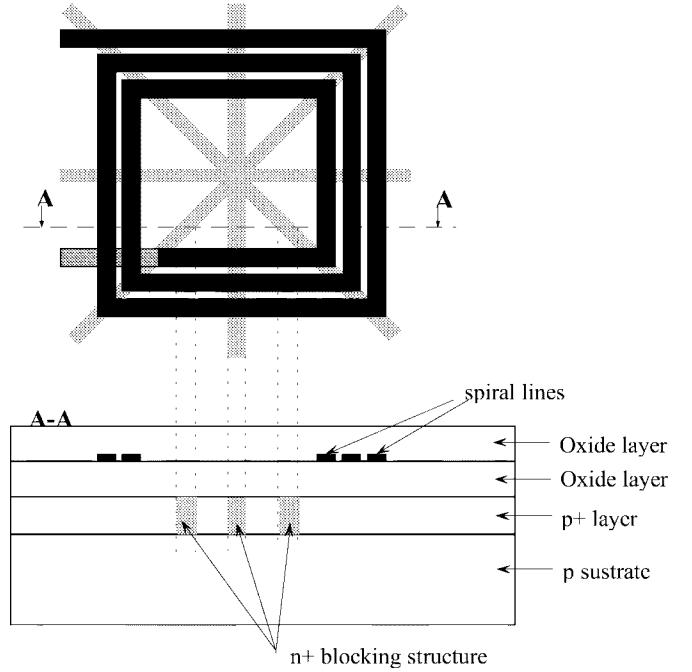

Since the substrate losses at the silicon substrates are related to its semiconductor nature we cannot easily reduce them. The losses are caused by the eddy currents induced by the magnetic field of the spirals. The eddy currents are flowing around the axis of the spiral. If we can reduce the eddy currents, the quality factor of the spirals will increase. With our BiCMOS technology, most of the substrate currents flow in the top heavily doped  $p+$  layer. This layer can be broken by  $n+$  regions. If we insert  $n+$  regions (narrow stripes) perpendicular to the eddy-current flow we create a blocking  $p-n-p$  junction

Fig. 1. Integrated spiral with eddy-current blocking structure.

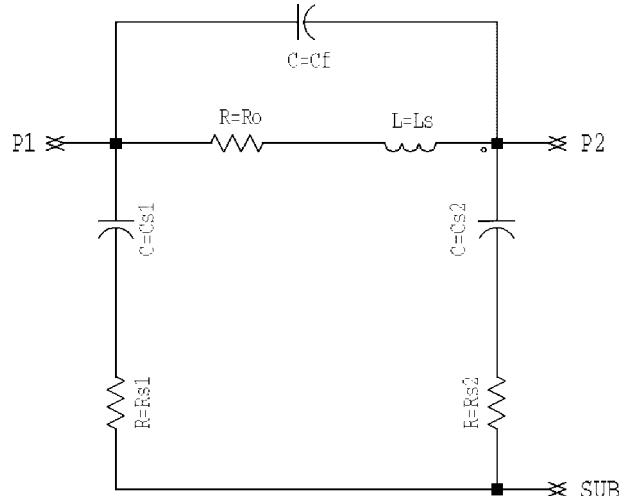

Fig. 2. The compact model of an integrated spiral.

against these currents. The layout of the spiral with the eddy-current blocking structure is shown on Fig. 1.

## III. MEASUREMENT RESULTS

To verify our idea we manufactured identical spirals with and without the blocking structure. We carried out S-parameter

Manuscript received April 20, 1998.

F. Mernyei is with the Budapest Design Office, Austria Mikro Systeme International AG, H-1135 Budapest, Hungary.

F. Darrer, M. Pardoen, and A. Sibrai are with the Engineering Department, Austria Mikro Systeme International AG, Schloß Premstätten, A-8141 Unterpremstätten, Austria.

Publisher Item Identifier S 1051-8207(98)07952-5.

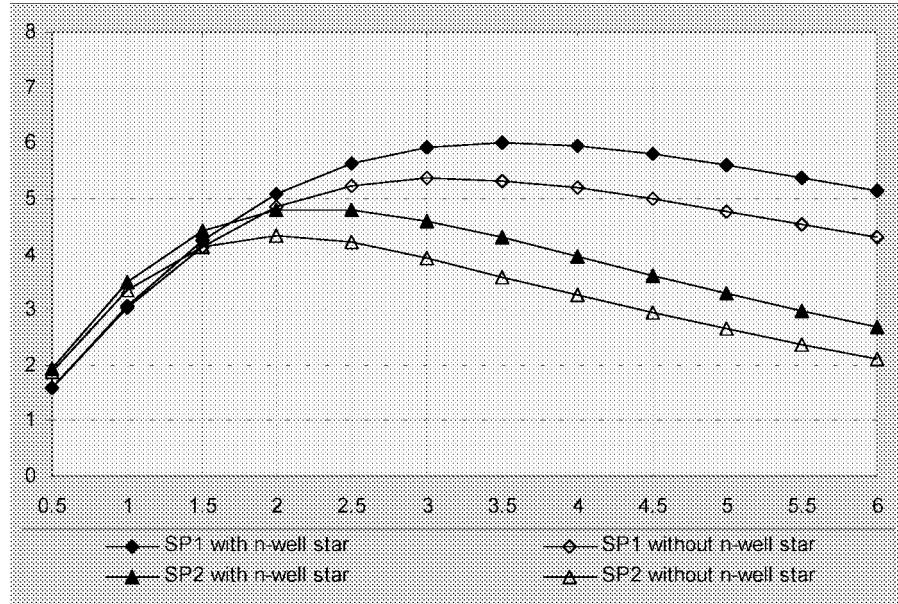

Fig. 3. Quality factor versus frequency at the measured inductors (see Table I for spiral details).

TABLE I

SPIRAL PARAMETERS

| Spirals             | SP1nw | SP1  | SP2nw | SP2  |

|---------------------|-------|------|-------|------|

| number of turns     | 2     | 2    | 3     | 3    |

| width of lines [μm] | 24    | 24   | 24    | 24   |

| Nwell struct.       | Yes   | No   | Yes   | No   |

| $L_s$ [nH]          | 1.81  | 1.80 | 2.82  | 2.81 |

| $C_f$ [fF]          | 23    | 14   | 49    | 51   |

| $C_{s1}$ [fF]       | 437   | 415  | 580   | 556  |

| $C_{s2}$ [fF]       | 334   | 383  | 428   | 458  |

| $R_{s1}$ [Ω]        | 308   | 291  | 354   | 338  |

| $R_{s2}$ [Ω]        | 522   | 399  | 429   | 335  |

| $f(Q_{max})$ [GHz]  | 3.5   | 3.5  | 2.0   | 2.0  |

| $Q_{max}$           | 6.0   | 5.3  | 4.8   | 4.3  |

| $R_o$ [Ω]           | 3.5   | 3.5  | 4.5   | 4.6  |

| $L_{eff}$ @ 2GHz    | 1.82  | 1.82 | 2.90  | 2.90 |

| $R_{eff}$ @ 2GHz    | 4.5   | 4.7  | 7.4   | 7.8  |

measurements on the spirals up to 6 GHz. By circuit optimization we extracted the parameters of the compact equivalent circuit (see Fig. 2). In Table I, the parameters of the spirals are summarized. Fig. 3 shows the quality factor of the spirals versus frequency, where we can see the improvement caused by the eddy-current blocking structure. We observed an increase from 5.3 to 6.0 at 3.5 GHz at an 1.8-nH inductor and from 4.3 to 4.8 at 2.2 GHz at an 2.8-nH inductor.

#### IV. CONCLUSIONS

A new method was introduced to improve the quality factor of the integrated spiral inductors at silicon RF IC's. The loss reduction is based on blocking the eddy currents in the semiconductive top p+ substrate layer with n+ stripes placed perpendicular to the eddy-current flow. The method was proved by measurements. With the described improvement our fully integrated voltage-controlled oscillator's (VCO's) phase noise performance became comparable with the ones having off-chip PCB resonators.

#### REFERENCES

- [1] K. B. Ashby, I. A. Koulias, W. C. Finley, J. J. Bastek, and S. Moinian, "High Q inductors for wireless application a complementary silicon bipolar process," *IEEE J. Solid-State Circuits*, vol. 31, pp. 4-9, Jan. 1996.

- [2] J. R. Long and M. A. Copeland, "The modeling, characterization, and design of monolithic inductors for silicon RF IC's," *IEEE J. Solid-State Circuits*, vol. 32, pp. 357-369, Mar. 1997.

- [3] J. Craninckx and M. S. J. Steyaert, "A 1.8 GHz low-phase-noise CMOS VCO using optimized hollow spiral inductors," *IEEE J. Solid-State Circuits*, vol. 32, pp. 736-744, May 1997.

- [4] B. Razavi, "Challenges in the design of frequency synthesizers for wireless applications," in *Proc. IEEE Custom Integrated Circuits Conf.*, 1997, pp. 395-402.

- [5] A. M. Niknejad and R. G. Meyer, "Analysis and optimization of monolithic inductors and transformers for RF IC's," *IEEE J. Solid-State Circuits*, vol. 32, pp. 375-378, May 1997.

- [6] J. Y. C. Chang, A. A. Abidi, and M. Gaitan, "Large suspended inductors on silicon and their use in a 2 μm CMOS RF amplifier," *IEEE Electron Device Lett.*, vol. 14, pp. 246-248, May 1993.